# EXC-1553PCI/Px

MIL-STD-1553 Test and Simulation Board for PCI Systems

**User's Manual**

311 Meacham Avenue • Elmont, NY 11003 • Tel. (516) 327-0000 • Fax (516) 327-4645

e-mail: <a href="mailto:excalibur@mil-1553.com">excalibur@mil-1553.com</a>

website:

www.mil-1553.com

## Contents

| С | ntents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | i                      |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 1 | Introduction1-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                      |

|   | I.1 Overview1-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                      |

|   | I.2       Installation       1-         1.2.1       Software Installation       1-         1.2.2       Board Installation       1-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .3                     |

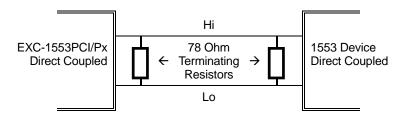

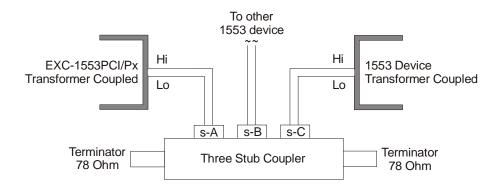

|   | 1.3 1553 Bus Connections1-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4                      |

| 2 | PCI Architecture2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                      |

|   | 2.1 Memory Structure2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                      |

|   | 2.2 PCI Configuration Space Header2-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                      |

|   | 2.3PCI Configuration Registers2-2.3.1Vendor Identification Register (VID)2-2.3.2Device Identification Register (DID)2-2.3.3PCI Command Register (PCICMD)2-2.3.4PCI Status Register (PCISTS)2-2.3.5Revision Identification Register (RID)2-2.3.6Class Code Register (CLCD)2-2.3.7Cache Line Size Register (CALN)2-2.3.8Latency Timer Register (LAT)2-2.3.9Header Type Register (HDR)2-2.3.10Built-In Self-Test Register (BIST)2-2.3.11Base Address Registers (BADR)2-2.3.12Cardbus CIS Pointer2-2.3.13Subsystem ID2-2.3.14Subvendor ID2-2.3.15Expansion ROM Base Address Register (XROM)2-2.3.18Interrupt Line Register (INTLN)2-2.3.19Minimum Grant Register (INTPIN)2-2.3.20Maximum Latency Register (MAXLAT)2-2.3.21Interrupt Status Register2- | 3345566666778888899990 |

| 3 | Bus Controller Operation3-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                        |

| 4 | Remote Terminal Operation4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                        |

|   | 4.1 RT Memory Map4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3                      |

|   | 4.2 Data Block Look-Up Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |

|   | 4.3 Active RT Table4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                      |

|   | 1.4 1553 RT Status Words4-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7                      |

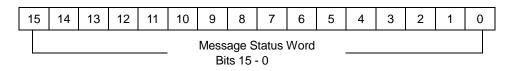

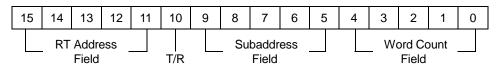

|   | 4.5       Message Stack       4-         4.5.1       Message Status Word       4-         4.5.2       Time Tag       4-1         4.5.3       1553 Command Word       4-1         4.5.4       RT-To-RT Messages       4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .9<br>0<br>0           |

|   | 4.6 RT Last Command Words                                                 |                |                                                           | 4-11         |

|---|---------------------------------------------------------------------------|----------------|-----------------------------------------------------------|--------------|

|   | 4.7                                                                       | 1553           | RT BIT Words                                              | 4-11         |

|   | 4.8                                                                       | 1553           | RT Vector Words                                           | 4-11         |

|   | 4.9                                                                       | Mode           | Codes                                                     | 4-12         |

|   | 4.10                                                                      | Bro            | adcast Mode                                               | 4-12         |

|   | 4.11                                                                      | Erro           | or Injection Features                                     | 4-13         |

|   | 4.11.1 Word Count Error Table                                             |                | Word Count Error Table                                    | 4-13         |

|   | 4.12                                                                      | Pro            | gram Example: RT Mode                                     | 4-14         |

|   | 4.13<br>4                                                                 | Cor<br>.13.1   | ntrol Register Definitions<br>Time Tag Options Register   | 4 <b>-15</b> |

|   |                                                                           | .13.2          | Time Tag Counter                                          |              |

|   |                                                                           | .13.3          | Time Tag Reset Register                                   |              |

|   |                                                                           | .13.4          | Options Select Register<br>Global Software Reset Register |              |

|   |                                                                           | .13.5<br>.13.6 | Interrupt Reset Register                                  |              |

|   |                                                                           | .13.7          | Software Reset Register                                   |              |

|   |                                                                           | .13.8          | Board Configuration Register                              |              |

|   |                                                                           | .13.9          | Board ID Register                                         |              |

|   | 4                                                                         | .13.10         | Board Status Register                                     |              |

|   |                                                                           | .13.11         | Start Register                                            |              |

|   | 4.13.12<br>4.13.13<br>4.13.14<br>4.13.15<br>4.13.16<br>4.13.17<br>4.13.18 |                | Message Status Register                                   |              |

|   |                                                                           |                | Time Tag Resolution Register                              |              |

|   |                                                                           |                | RT Response Time Register<br>Error Injection Register     |              |

|   |                                                                           |                | Message Stack Pointer                                     |              |

|   |                                                                           |                | Status Response Register                                  |              |

|   |                                                                           |                | Board Options Register                                    |              |

|   |                                                                           | .13.19         | Firmware Revision Register                                | 4-21         |

|   |                                                                           | .13.20         | Interrupt Condition Register                              |              |

|   | 4                                                                         | .13.21         | Mode Code Control Register                                | 4-22         |

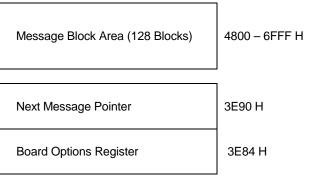

| 5 | E                                                                         | SC/Co          | ncurrent-RT Operation                                     | 5-1          |

|   | 5.1                                                                       | BC/C           | oncurrent-RT Memory Map                                   | 5-3          |

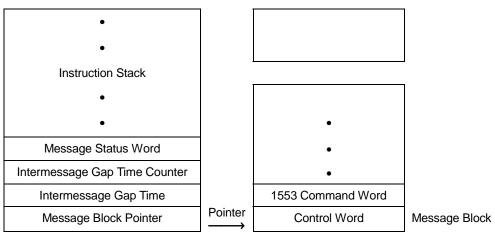

|   | 5.2                                                                       |                | iction Stack                                              |              |

|   | 5.                                                                        | .2.1<br>.2.2   | Message Status Word<br>Intermessage Gap Time              | 5-5<br>5 6   |

|   |                                                                           | .2.2           | Intermessage Gap Time Counter                             |              |

|   |                                                                           | .2.4           | Message Block Pointer                                     |              |

|   |                                                                           | .2.5           | Message Block                                             |              |

|   | 5                                                                         | .2.6           | Control Word                                              | 5-8          |

|   |                                                                           | .2.7           | Halt Operation                                            |              |

|   |                                                                           | .2.8           | Skip Message Operation                                    |              |

|   |                                                                           | .2.9           | Jump Command Operation                                    |              |

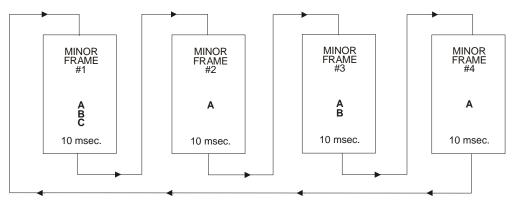

|   |                                                                           | .2.10<br>.2.11 | Minor Frame Operation<br>Asynchronous Frame Operation     |              |

|   | 5.3                                                                       |                | ote Terminal Simulation                                   |              |

|   | 5.4                                                                       |                | age Block Formats                                         |              |

|   |                                                                           |                |                                                           |              |

|   | 5.5<br>5.                                                                 | Contil<br>.5.1 | nuous or One-Shot Message Transfers                       |              |

|   | 5.6                                                                       | Progr          | am Example: BC/Concurrent-RT Mode                         | 5-17         |

|   | 5.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Contr                                                                                                                                               | ol Register Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-18                                                                                                                                                     |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .7.1                                                                                                                                                | Options Select Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-18                                                                                                                                                     |

|   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .7.2                                                                                                                                                | Global Software Reset Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                          |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .7.3                                                                                                                                                | Interrupt Reset Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                          |

|   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .7.4                                                                                                                                                | Software Reset Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                          |

|   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .7.5                                                                                                                                                | Board Configuration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                          |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .7.6                                                                                                                                                | Board ID Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                          |

|   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .7.7                                                                                                                                                | Board Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                          |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .7.8<br>.7.9                                                                                                                                        | Start Register<br>Interrupt Condition Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                          |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .7.10                                                                                                                                               | Message Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                          |

|   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .7.10                                                                                                                                               | RT Response Time Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-22                                                                                                                                                     |

|   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .7.12                                                                                                                                               | Loop Count Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                          |

|   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .7.13                                                                                                                                               | Bit Count Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                          |

|   | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .7.14                                                                                                                                               | Word Count Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                          |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .7.15                                                                                                                                               | BC Response Time Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-26                                                                                                                                                     |

|   | 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .7.16                                                                                                                                               | Stack Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                          |

|   | 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .7.17                                                                                                                                               | Frame Time Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                          |